Verilog代码中低有效信号的写法可以通过以下3个关键点来实现:1、使用反相(~)操作符,2、在敏感列表中明确表示低有效信号,3、在逻辑条件中明确低有效信号的判断。低有效信号(active low)是指信号为低电平(0)时被激活,而高电平(1)时不激活。以下是详细的描述和一些示例代码来帮助理解。

一、低有效信号的定义与操作

1、反相操作符:在Verilog中,可以使用反相操作符()来表示低有效信号。例如,如果一个复位信号reset_n是低有效的,当reset_n为0时,系统复位。当reset_n为1时,系统正常运行。

2、敏感列表:在Always块的敏感列表中,明确表示低有效信号。这样可以确保在低有效信号改变时触发相应的行为。

3、逻辑条件:在逻辑条件中,明确判断低有效信号的状态,比如if (reset_n)表示在reset_n为低电平时执行复位逻辑。

示例代码:

module low_active_example (

input wire clk,

input wire reset_n, // Active low reset

output reg [7:0] counter

);

always @(posedge clk or negedge reset_n) begin

if (~reset_n)

counter <= 8'b0; // Reset counter to 0 when reset_n is low

else

counter <= counter + 1; // Increment counter on each clock cycle

end

endmodule

二、使用低有效信号的原因和优势

1、噪声免疫力:低有效信号在硬件设计中更能抵抗噪声干扰。在集成电路中,电源噪声和地噪声的影响不同,低电平信号相对高电平信号更不容易受到电源噪声的干扰。

2、电源和地的逻辑设计:在逻辑设计中,使用低有效信号可以更好地管理电源和地的连接。许多芯片内部的逻辑电路更容易实现低电平信号的检测和处理。

3、节省功耗:低有效信号在某些情况下可以节省功耗。例如,在复位电路中,使用低有效信号可以减少复位电路的功耗,因为大多数时间复位信号处于高电平,电路不会消耗额外的功率。

三、低有效信号的常见应用

1、复位信号:复位信号通常设计为低有效。原因是,在电源上电或复位状态下,复位信号为低电平,可以确保系统所有部分都被正确复位。

2、使能信号:一些使能信号也设计为低有效。例如,芯片选择信号(chip select, CS)在许多存储器和外设中是低有效的。

3、中断信号:在某些微处理器和控制器中,中断信号也设计为低有效,以便在中断发生时立即触发相应的处理逻辑。

示例代码:

module active_low_signals (

input wire clk,

input wire rst_n, // Active low reset

input wire cs_n, // Active low chip select

input wire irq_n, // Active low interrupt request

output reg [7:0] data

);

always @(posedge clk or negedge rst_n) begin

if (~rst_n)

data <= 8'b0; // Reset data to 0 when rst_n is low

else if (~cs_n)

data <= 8'b10101010; // Load specific data when cs_n is low

else if (~irq_n)

data <= 8'b11110000; // Load interrupt-specific data when irq_n is low

else

data <= data + 1; // Increment data on each clock cycle

end

endmodule

四、低有效信号的设计注意事项

1、明确的信号命名:为了避免混淆,低有效信号的名称通常带有后缀_n或_b。例如,reset_n或reset_b表示低有效复位信号。这有助于在设计和调试过程中明确信号的行为。

2、时序分析:在时序分析中,需要特别注意低有效信号的时序要求。确保在信号转换过程中不会引入不必要的延迟或毛刺。

3、文档和注释:在代码中添加详细的注释和文档,说明低有效信号的使用和意图。这有助于其他设计者理解和维护代码。

总结:

低有效信号在Verilog设计中广泛应用,具有噪声免疫力强、电源和地逻辑设计方便、节省功耗等优点。通过合理的设计和使用,可以提高系统的可靠性和性能。在实际应用中,务必注意信号命名、时序分析和文档注释等方面的细节,确保设计的正确性和可维护性。

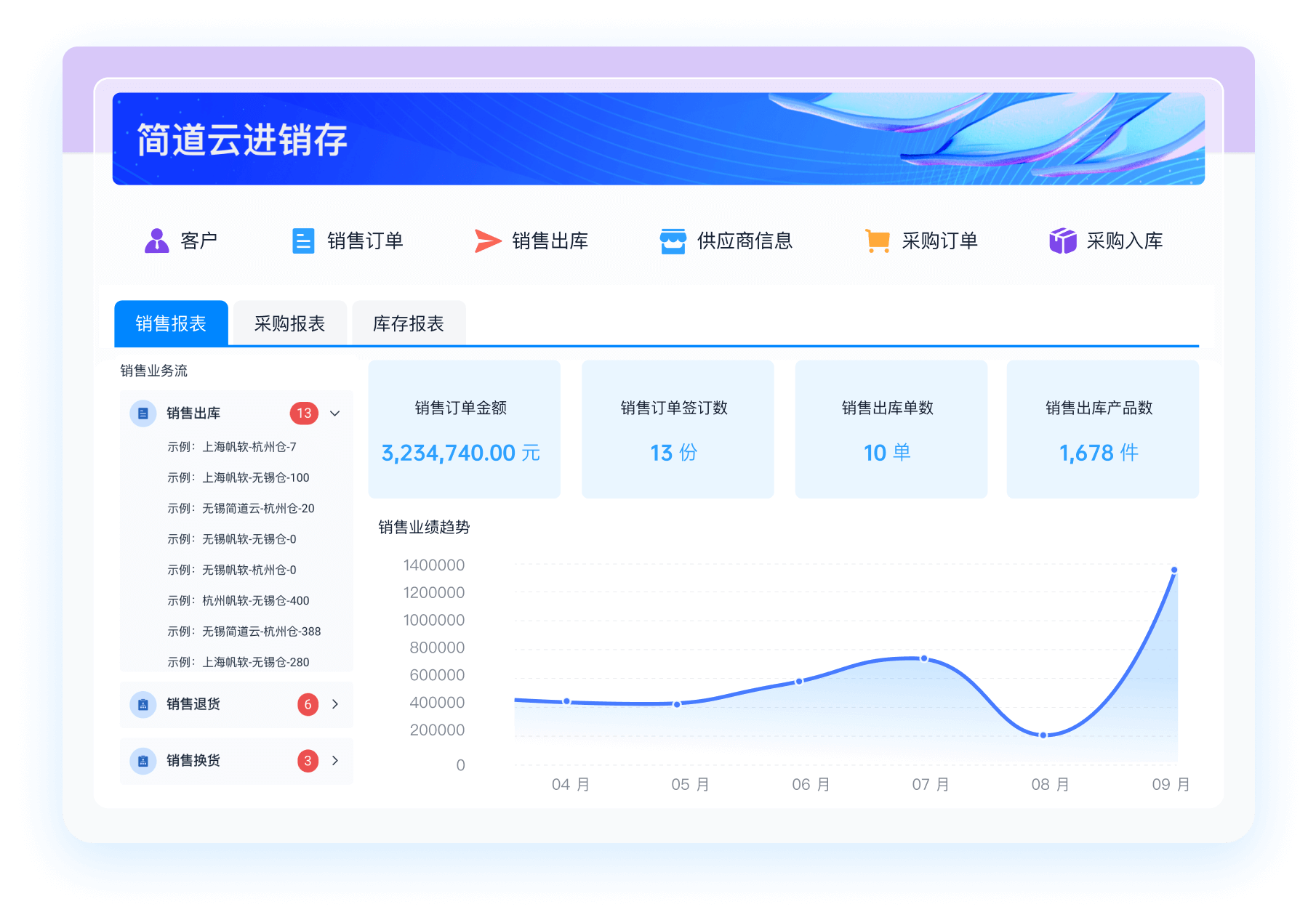

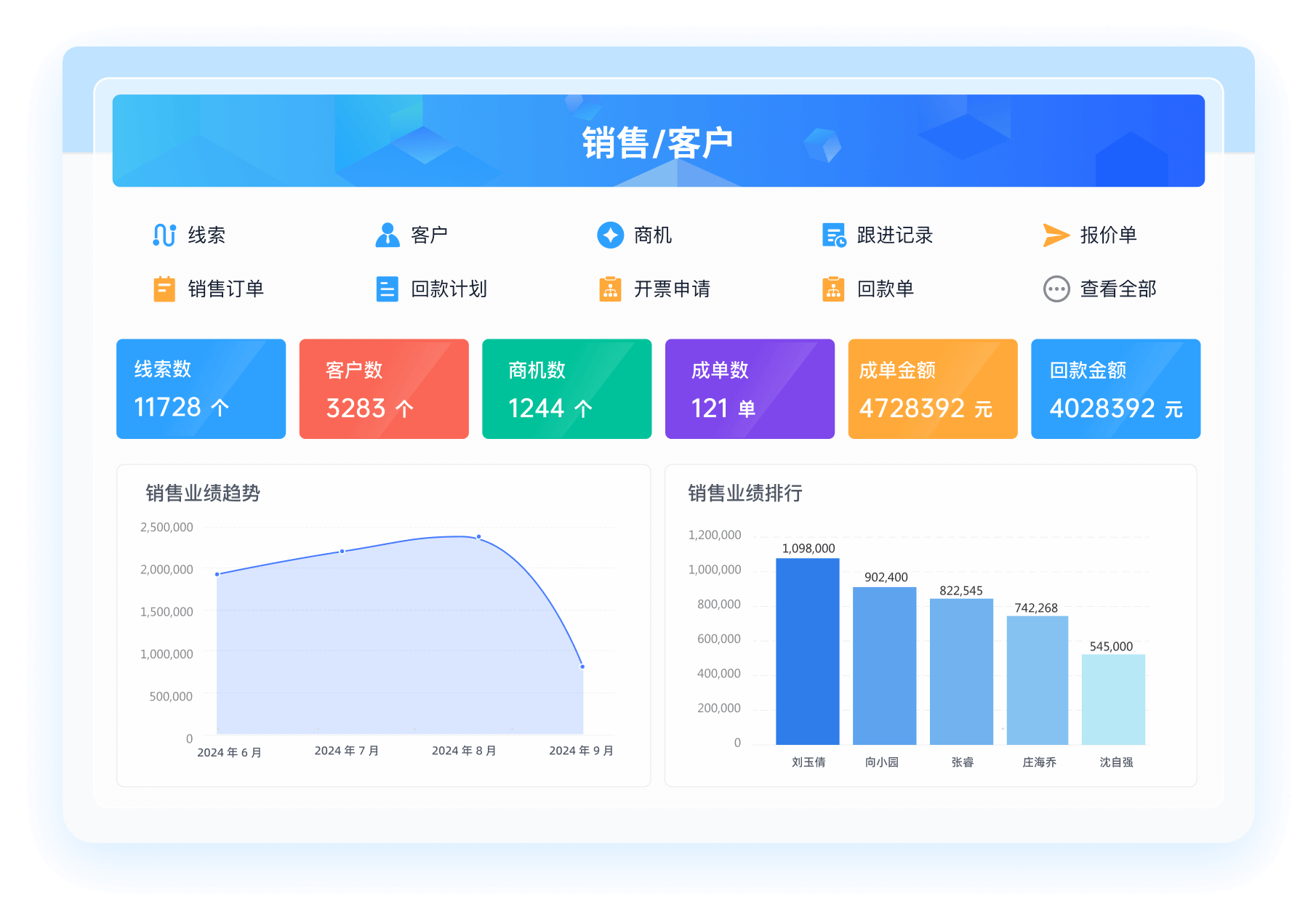

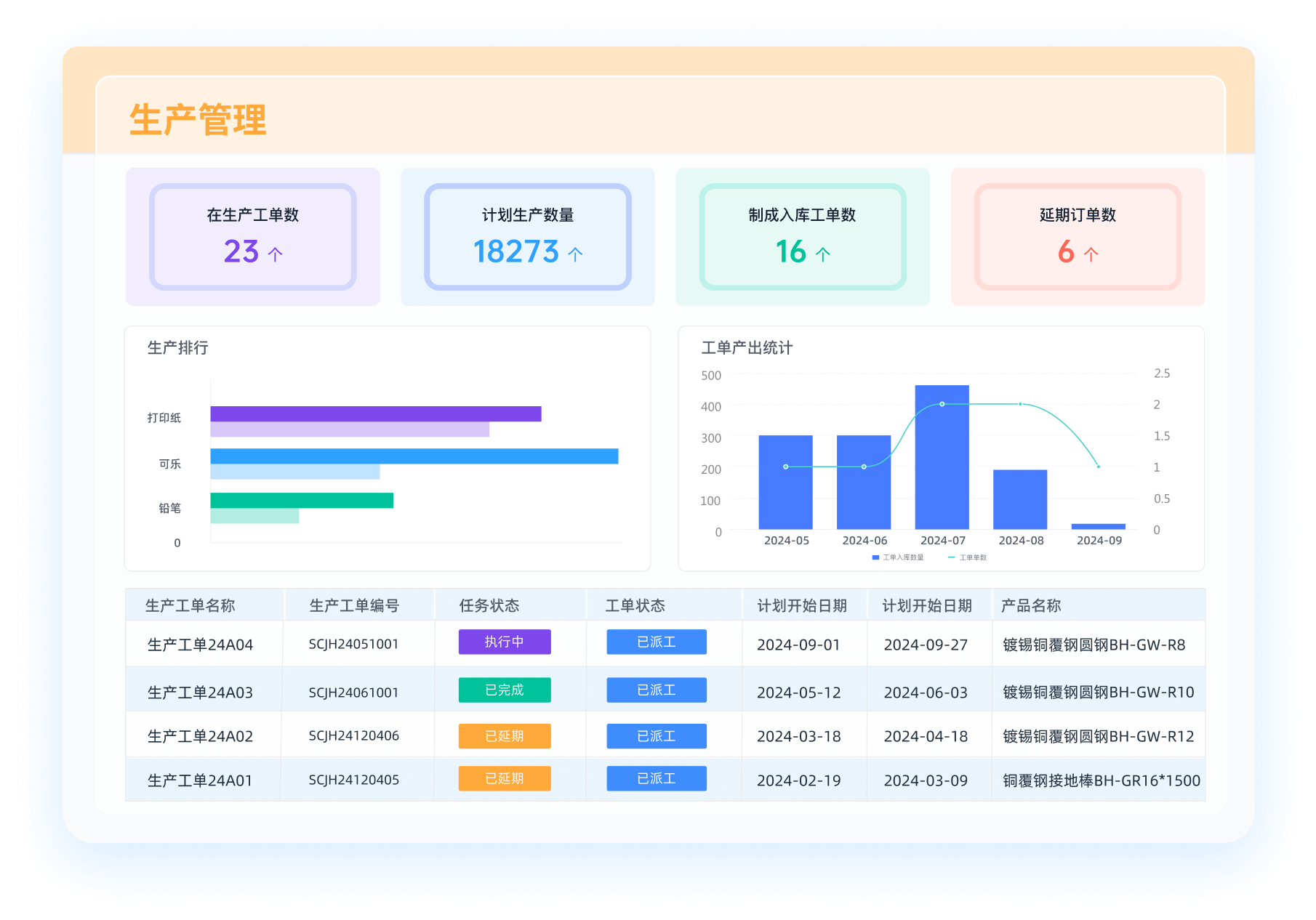

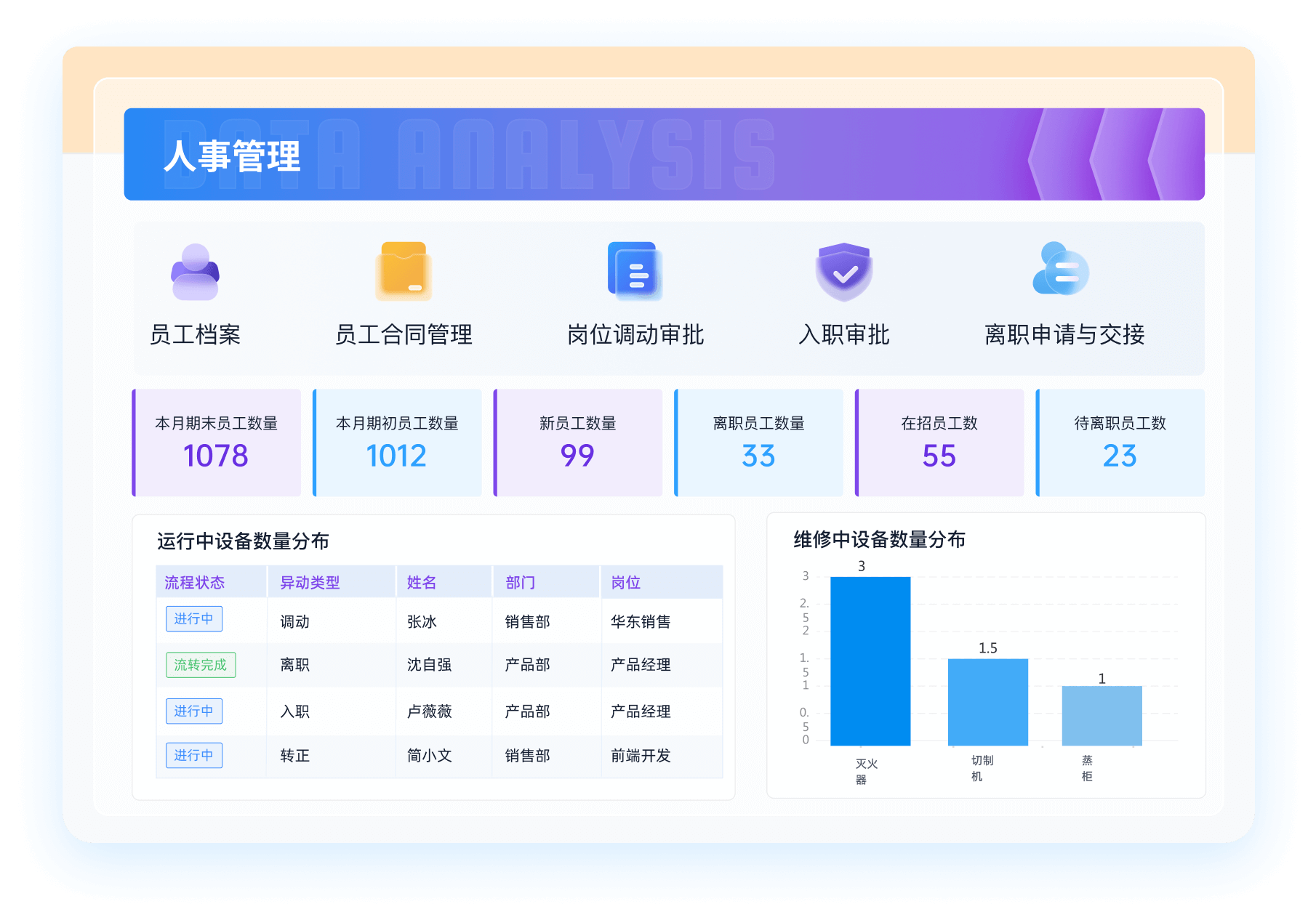

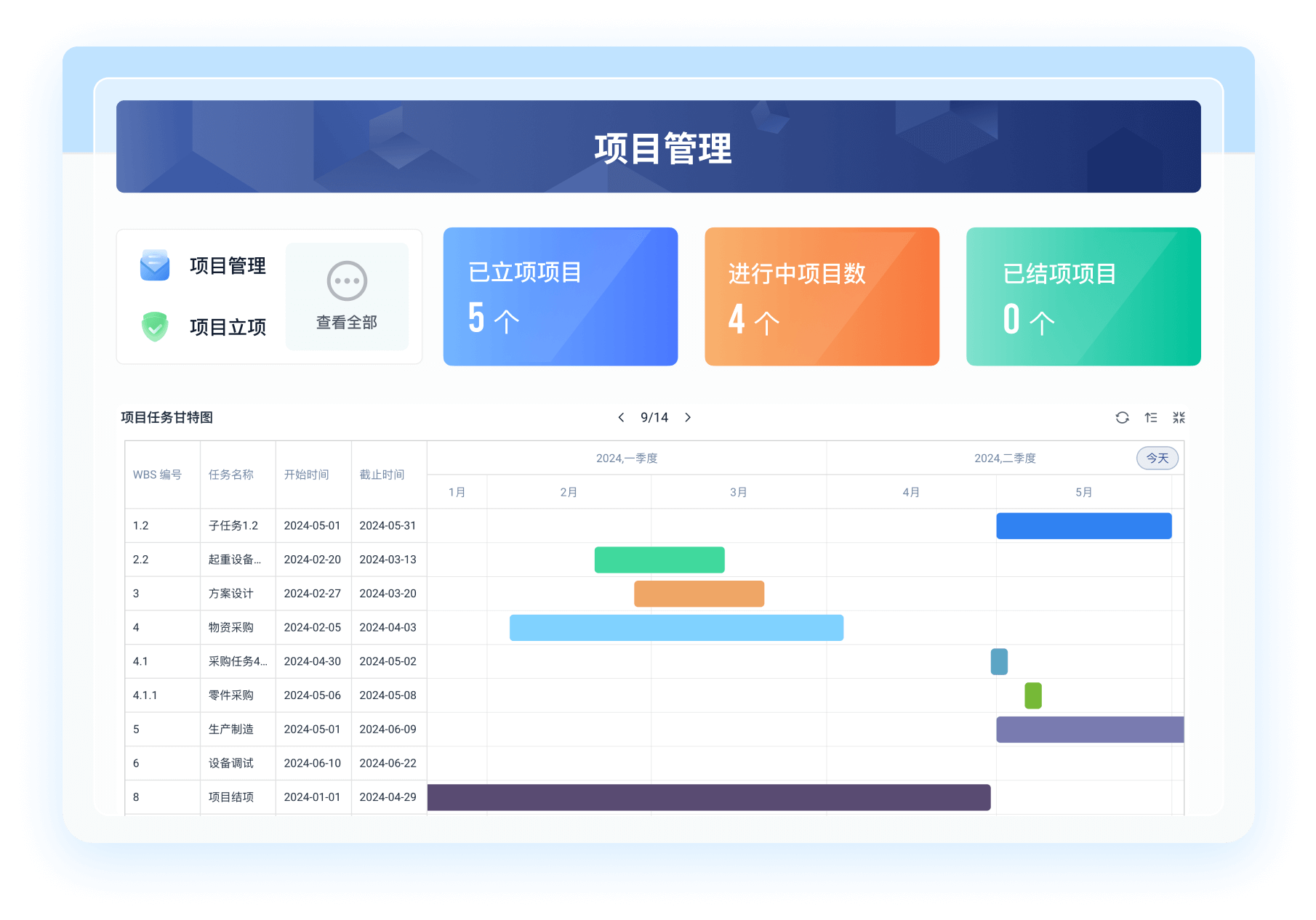

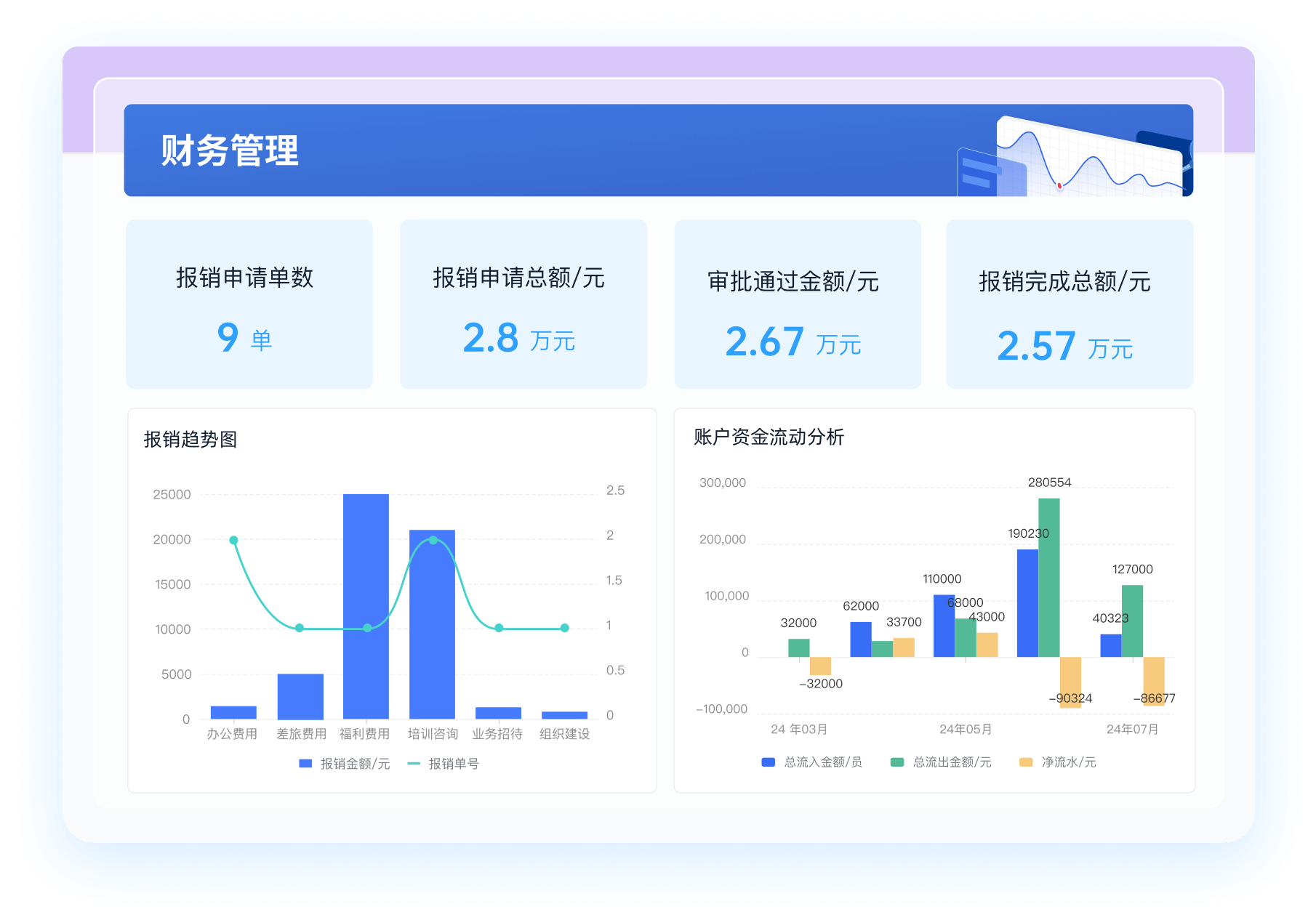

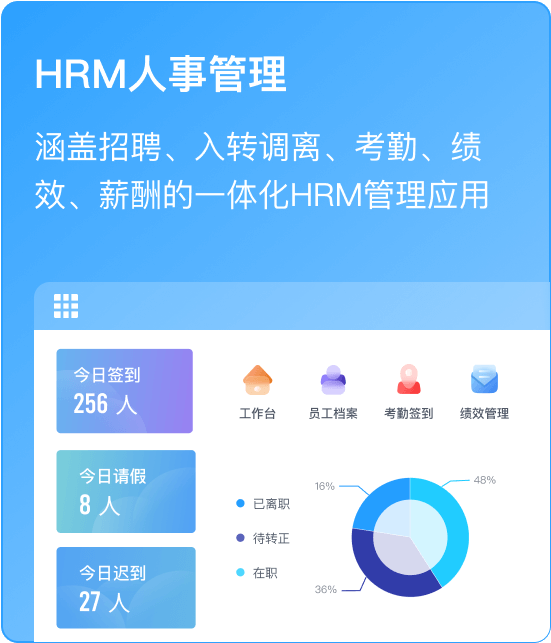

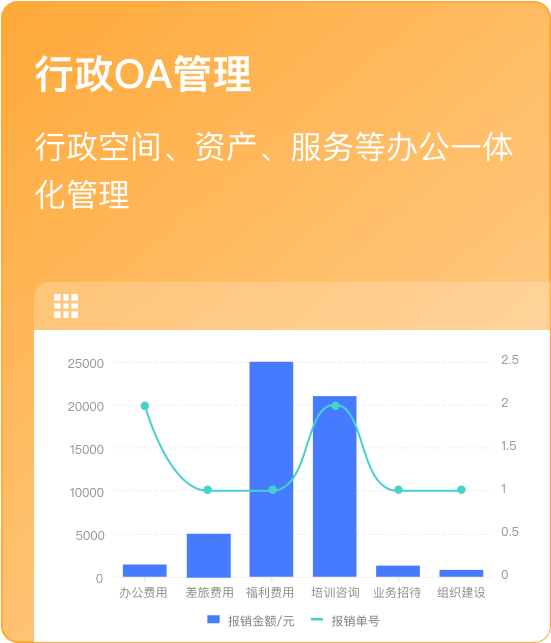

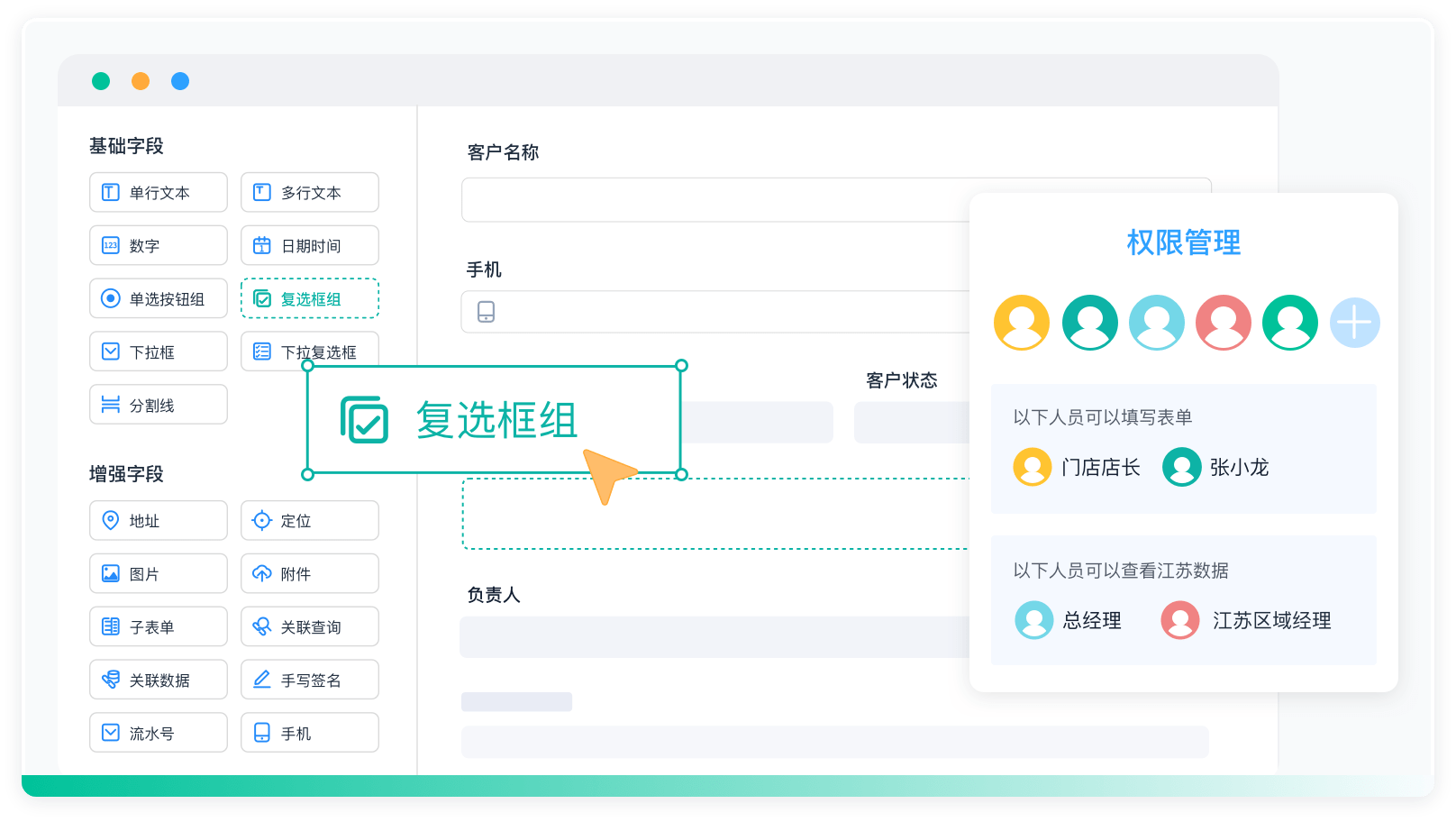

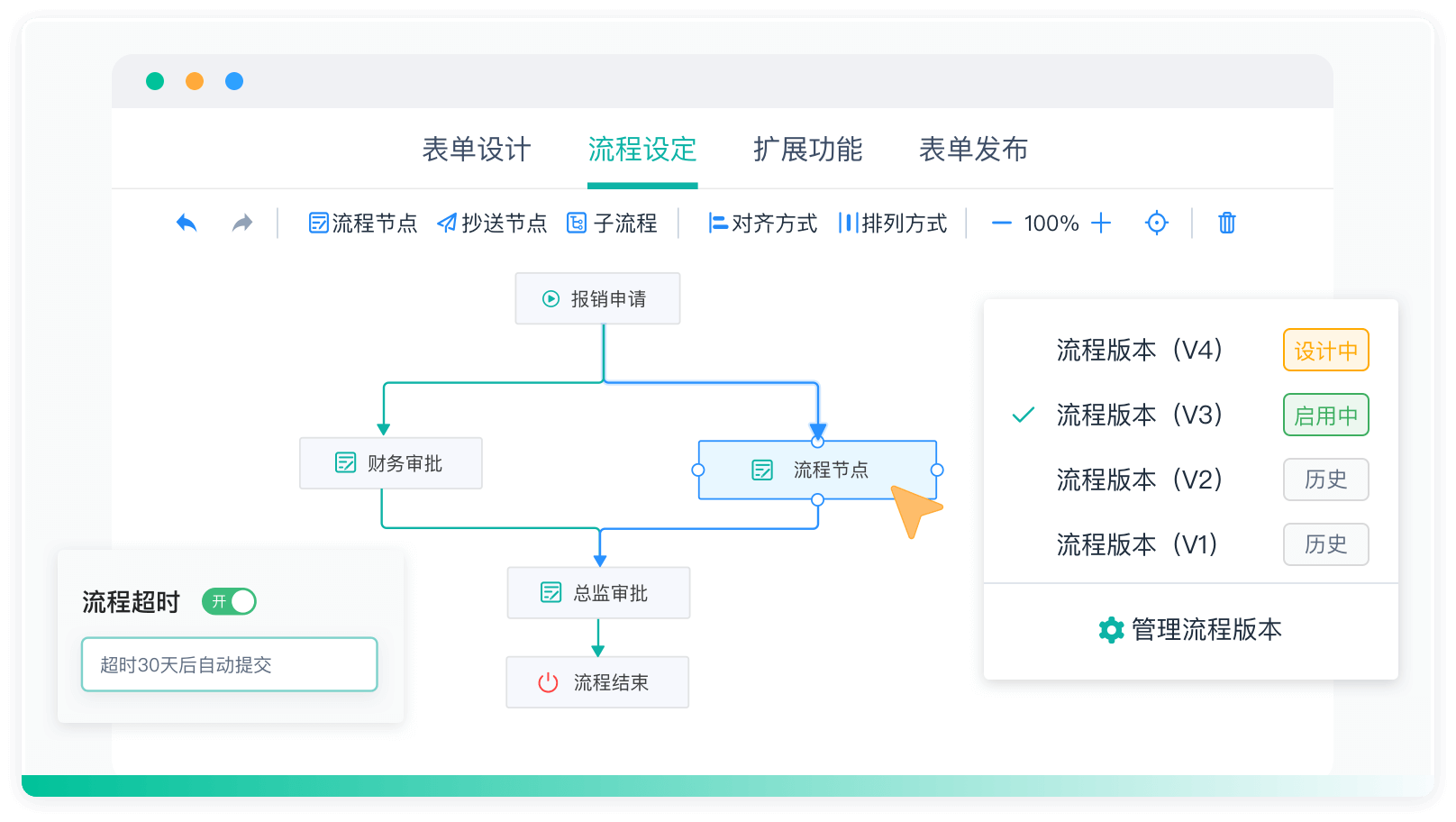

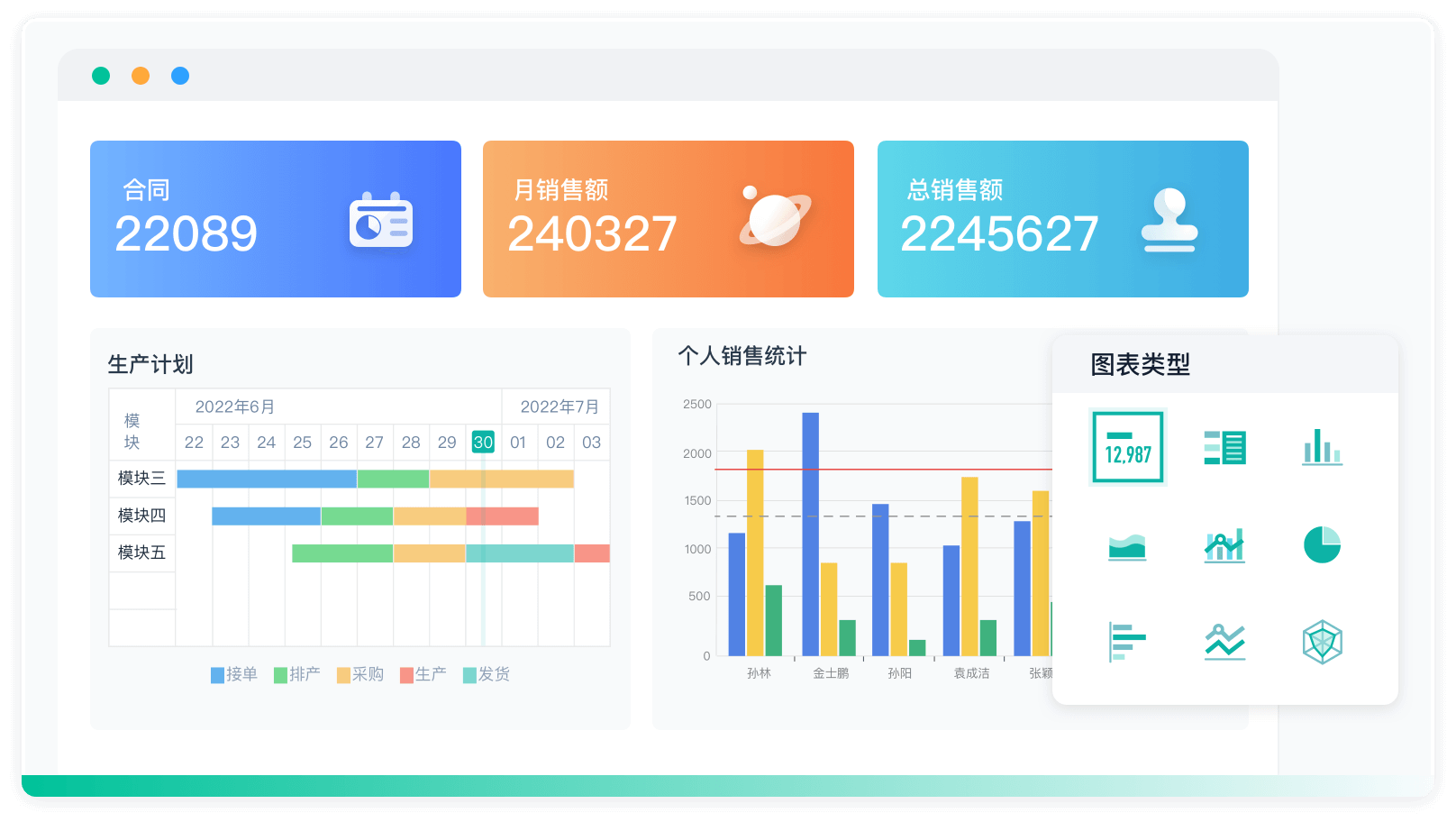

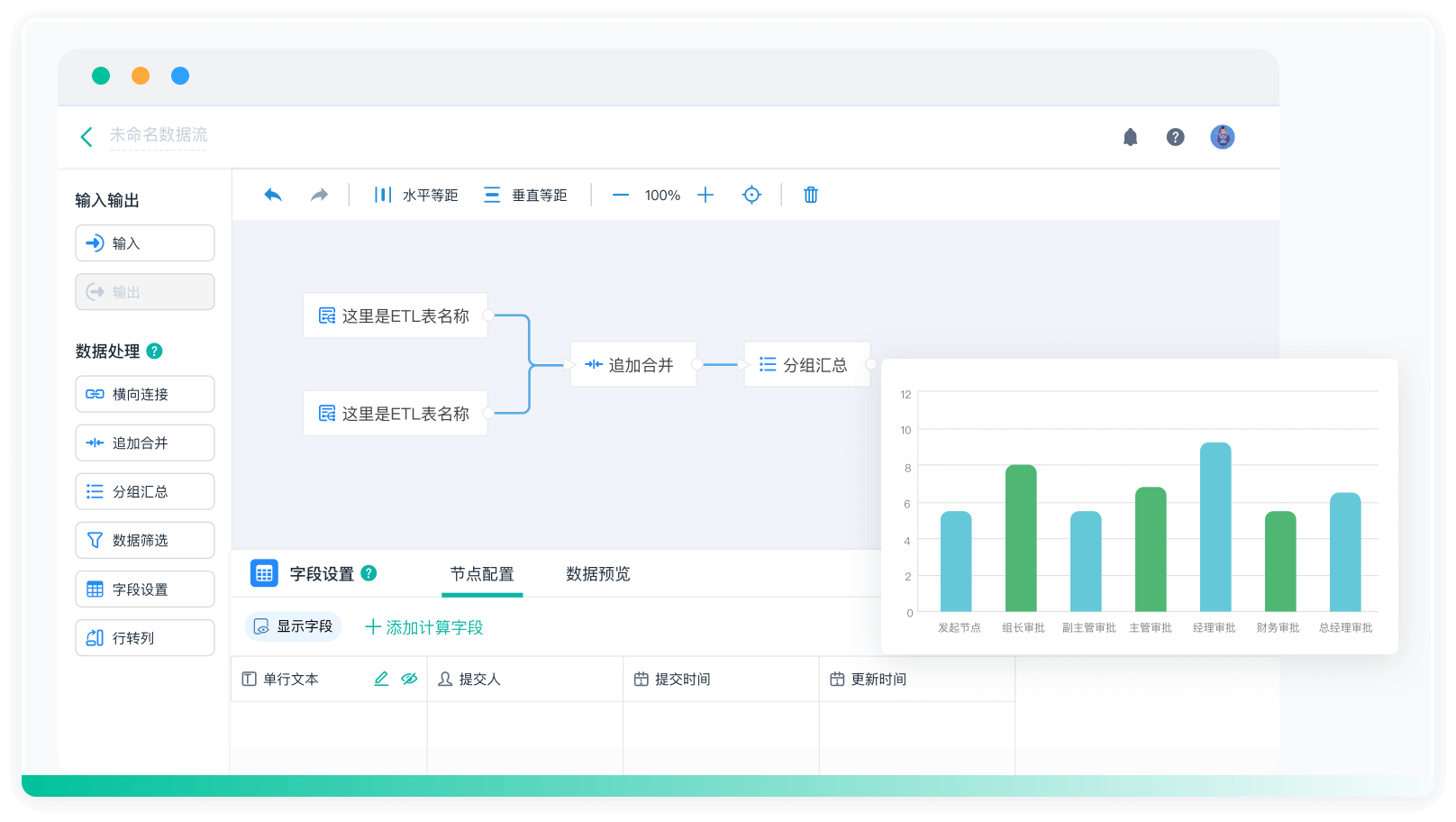

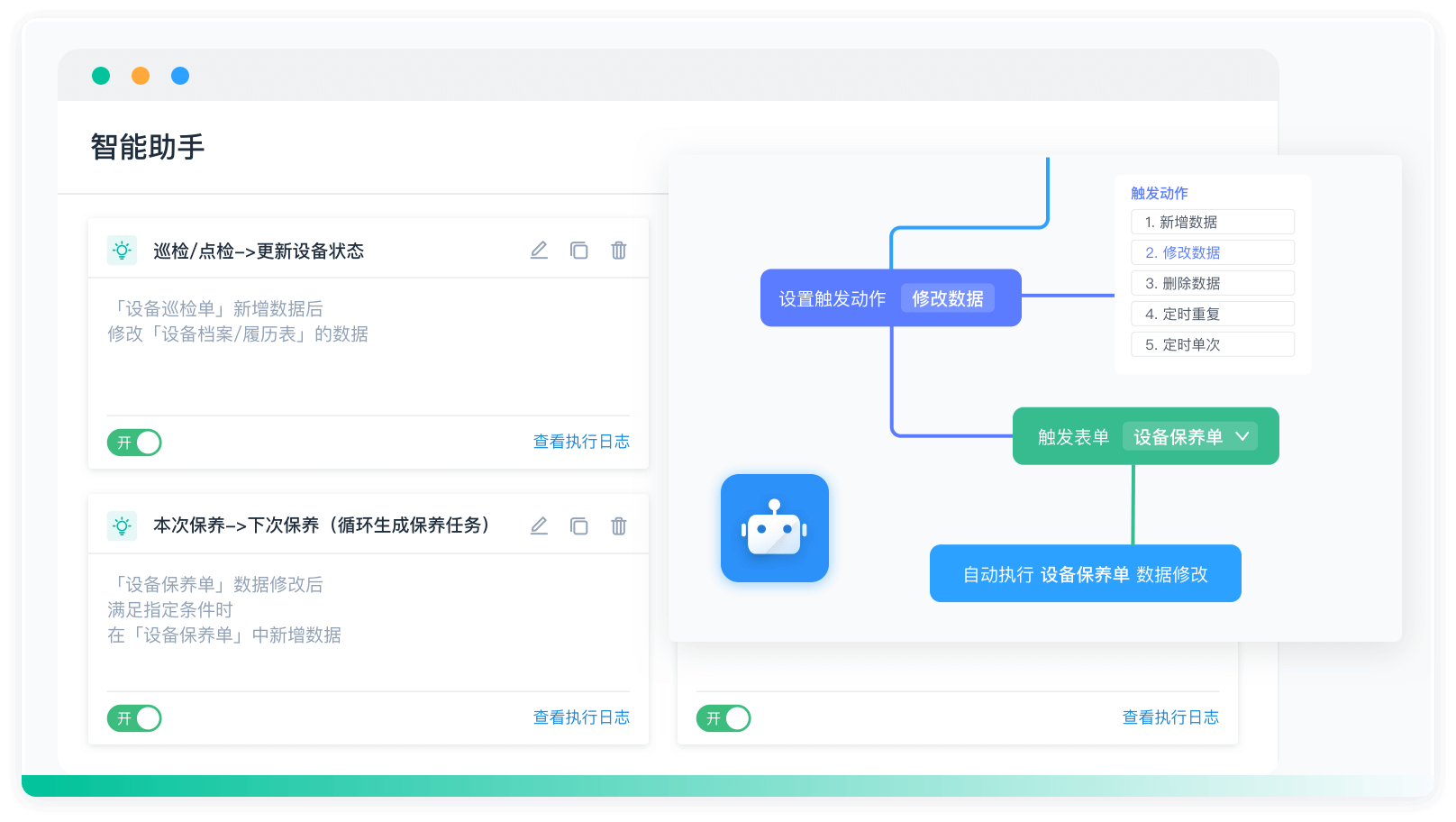

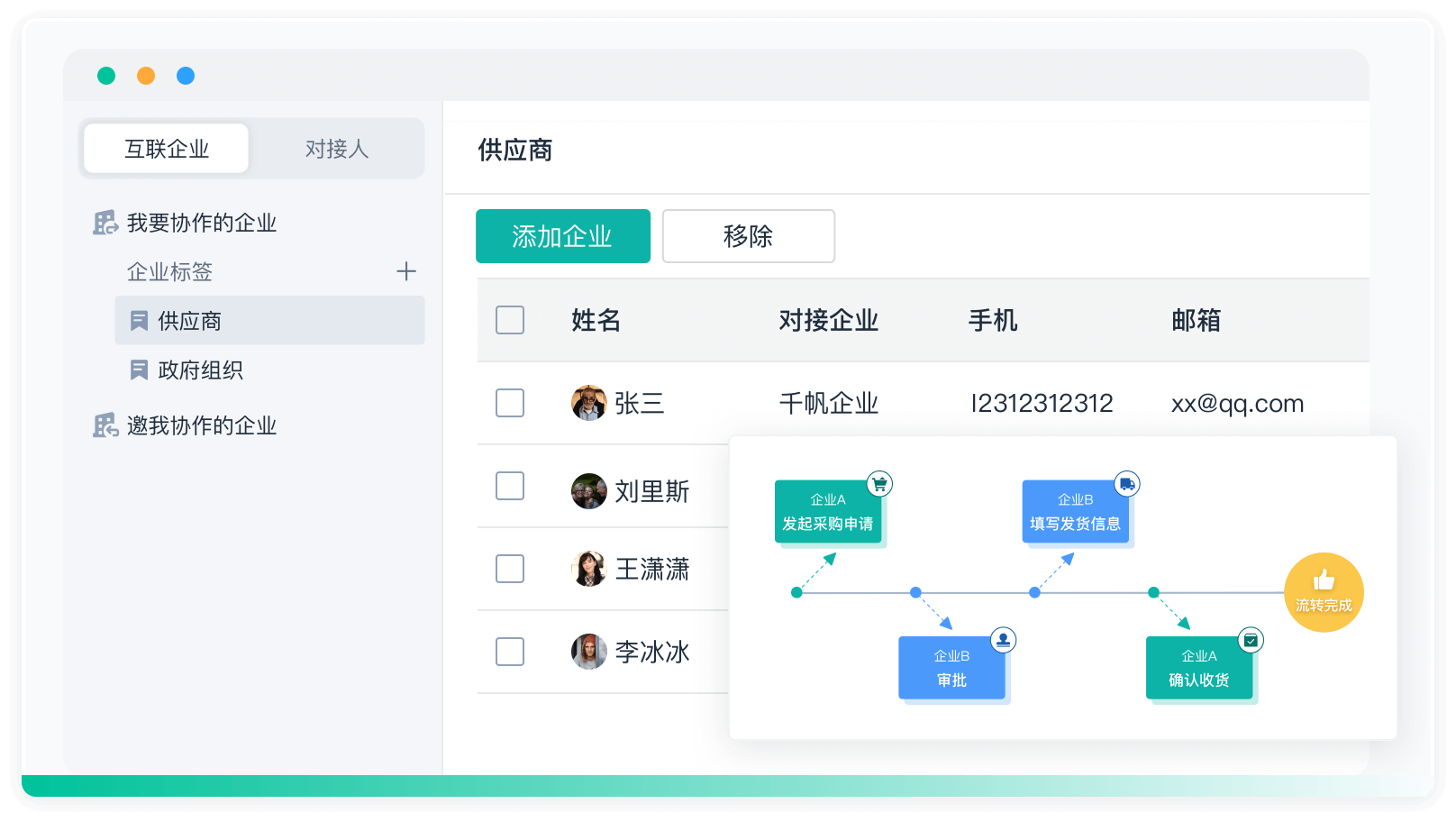

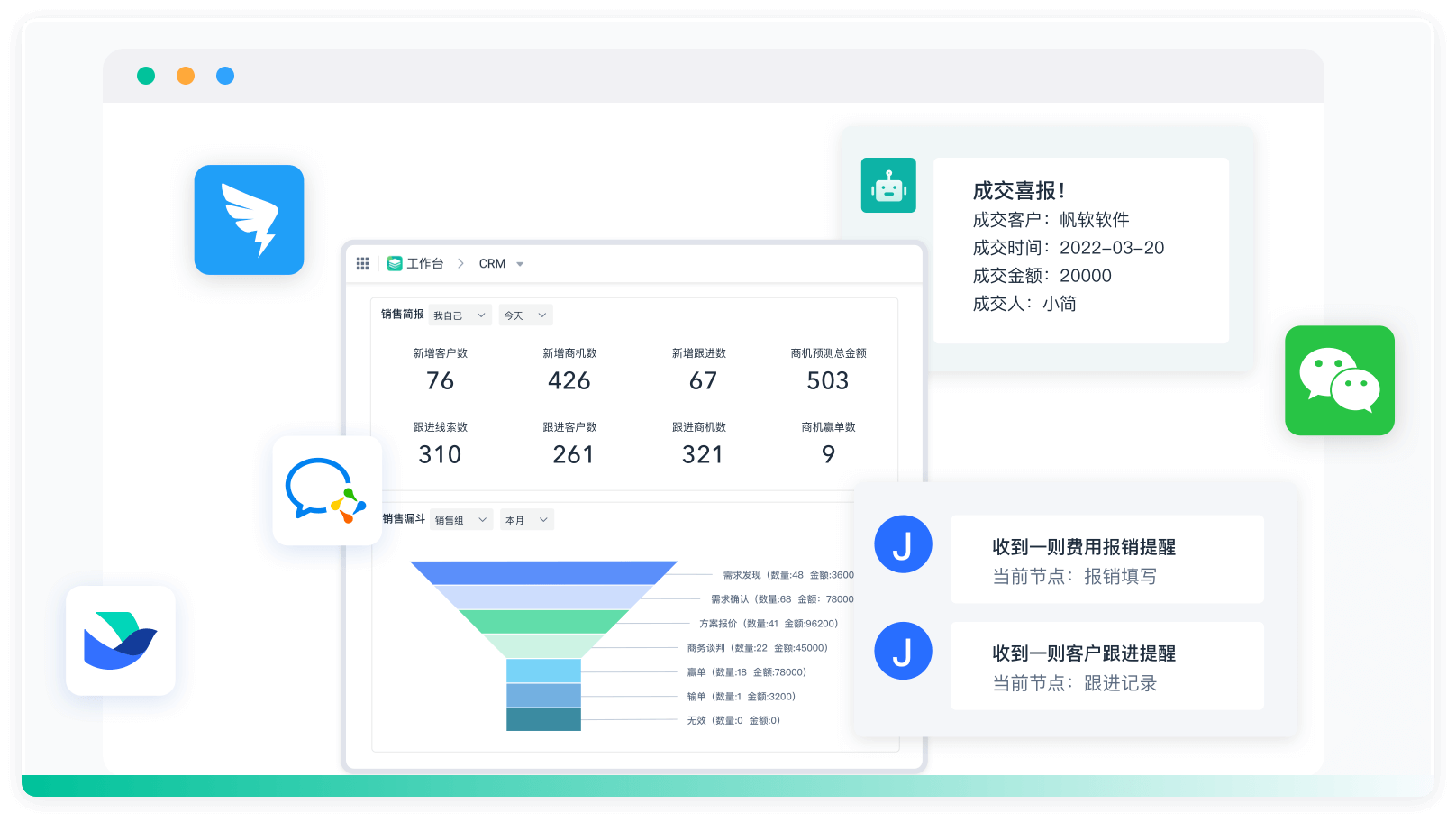

简道云低代码平台是一个高效的工具,可以帮助开发者快速实现各种信号处理和逻辑设计。更多信息请访问简道云低代码官网: https://s.fanruan.com/x6aj1;。

相关问答FAQs:

如何在Verilog中实现低有效信号的控制?

在Verilog中,低有效信号通常指的是逻辑信号在低电平(0)时被认为是有效状态。这在设计数字电路时非常常见,尤其是在控制信号和复位信号中。为了实现这一点,设计者可以使用适当的逻辑操作和条件语句来响应低有效信号。

例如,如果你想要一个低有效的复位信号,可以这样编写代码:

module example (

input wire reset_n, // 低有效复位信号

input wire clk,

output reg out

);

always @(posedge clk or negedge reset_n) begin

if (!reset_n) begin

out <= 0; // 当reset_n为低时,out被清零

end else begin

out <= 1; // 正常工作状态

end

end

endmodule

在这个例子中,reset_n是一个低有效信号。当它为0时,out信号会被设置为0。这个实现方式确保了设计者可以轻松地控制低有效信号的行为。

低有效信号在Verilog中的常见应用场景有哪些?

低有效信号在数字电路设计中有多种应用场景,包括但不限于复位信号、使能信号和中断信号。对于复位信号,通常在系统启动或发生异常时将系统状态清零。使能信号则控制数据流的开关,只有在使能信号为高时,数据才会通过,而低状态则阻止数据流动。在中断信号处理中,低有效信号可以用来表示某种事件的发生,从而触发相应的处理逻辑。

如何在Verilog中使用低有效信号进行状态机设计?

在状态机设计中,低有效信号通常用于状态转换或条件判断。设计者可以使用状态编码和逻辑判断来处理低有效信号。例如,以下是一个简单的状态机例子,其中使用了低有效的使能信号:

module fsm (

input wire clk,

input wire enable_n, // 低有效使能信号

output reg state

);

typedef enum reg {S0, S1} state_t;

state_t current_state, next_state;

always @(posedge clk or negedge enable_n) begin

if (!enable_n) begin

current_state <= S0; // 使能信号为低时,返回初始状态

end else begin

current_state <= next_state; // 状态转换

end

end

always @* begin

case (current_state)

S0: next_state = S1;

S1: next_state = S0;

default: next_state = S0;

endcase

end

endmodule

在这个示例中,enable_n作为低有效使能信号,在其为0时,状态机会重置到初始状态S0。

推荐

如果你希望快速构建管理软件而无需编写代码,推荐使用零代码开发平台,它可以在短短5分钟内帮助你搭建一个管理软件。了解更多内容,请访问:零代码开发平台。

如果你正在寻找企业管理系统模板,100多种企业管理系统模板可供免费使用,无需下载,支持在线安装。请查看这里:企业管理系统模板。

阅读时间:5 分钟

阅读时间:5 分钟  浏览量:2159次

浏览量:2159次

《零代码开发知识图谱》

《零代码开发知识图谱》

《零代码

新动能》案例集

《零代码

新动能》案例集

《企业零代码系统搭建指南》

《企业零代码系统搭建指南》